Xây dựng thuật toán, thử nghiệm đánh giá mô hình cứng hóa giao thức IKEv2.0

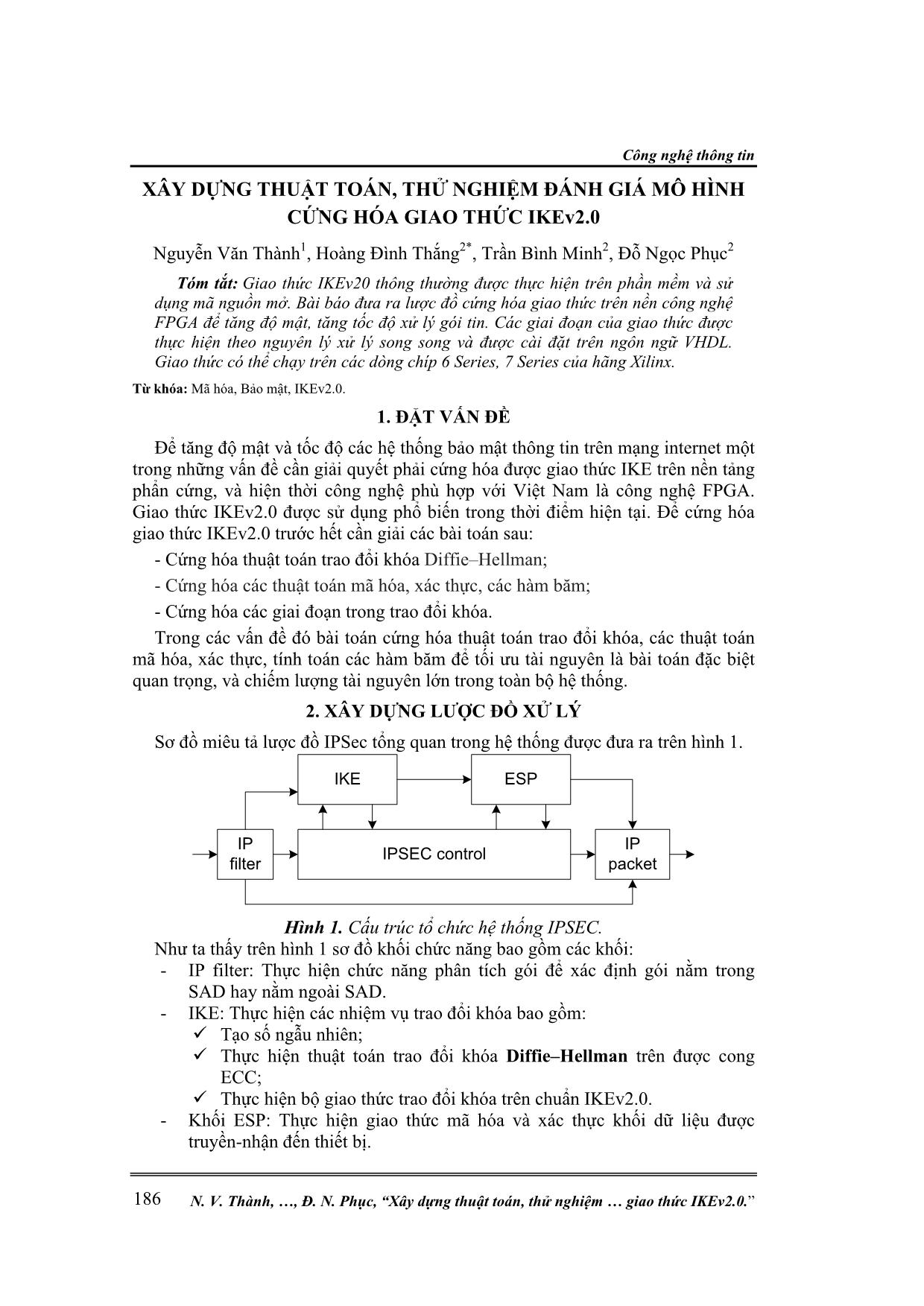

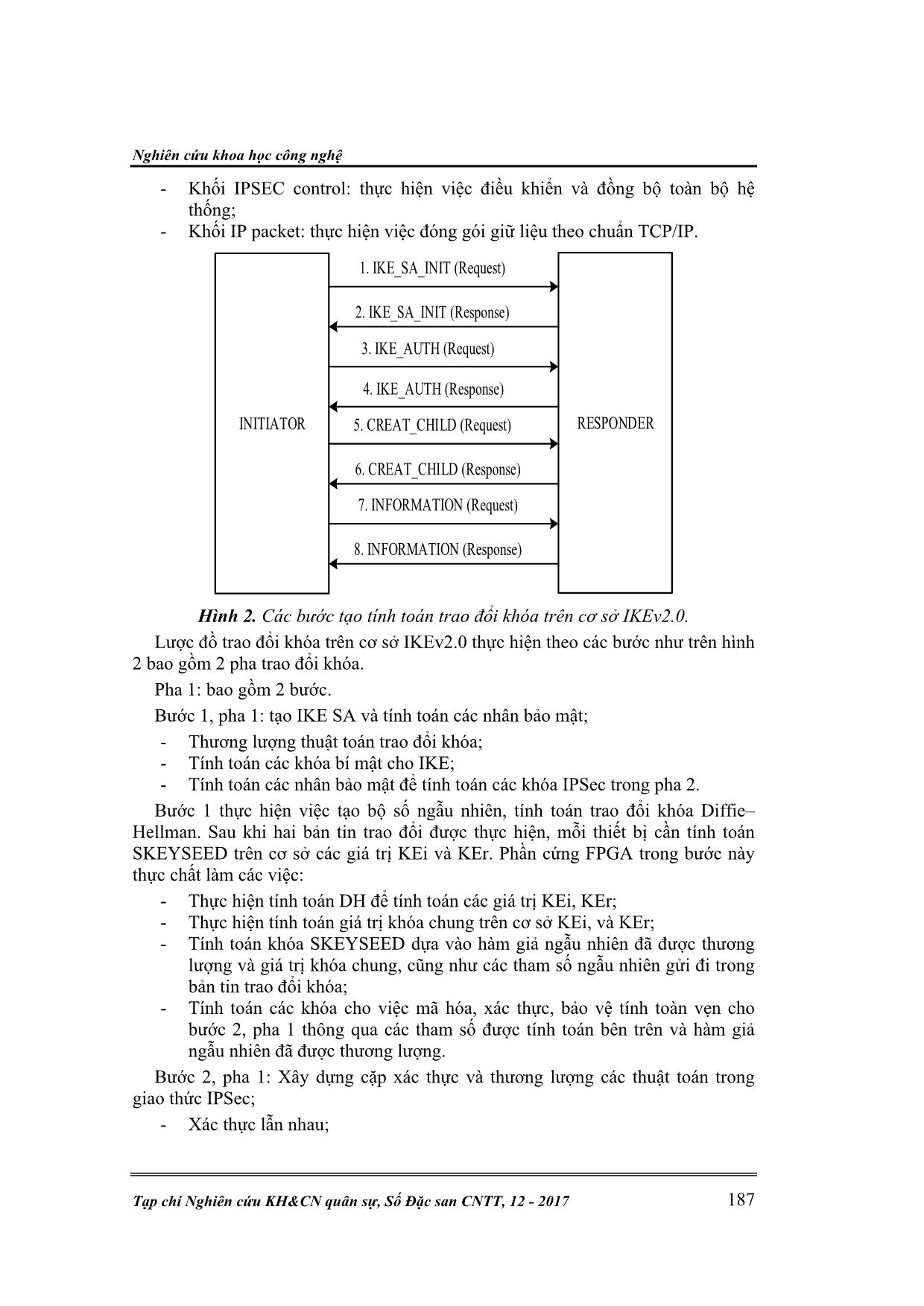

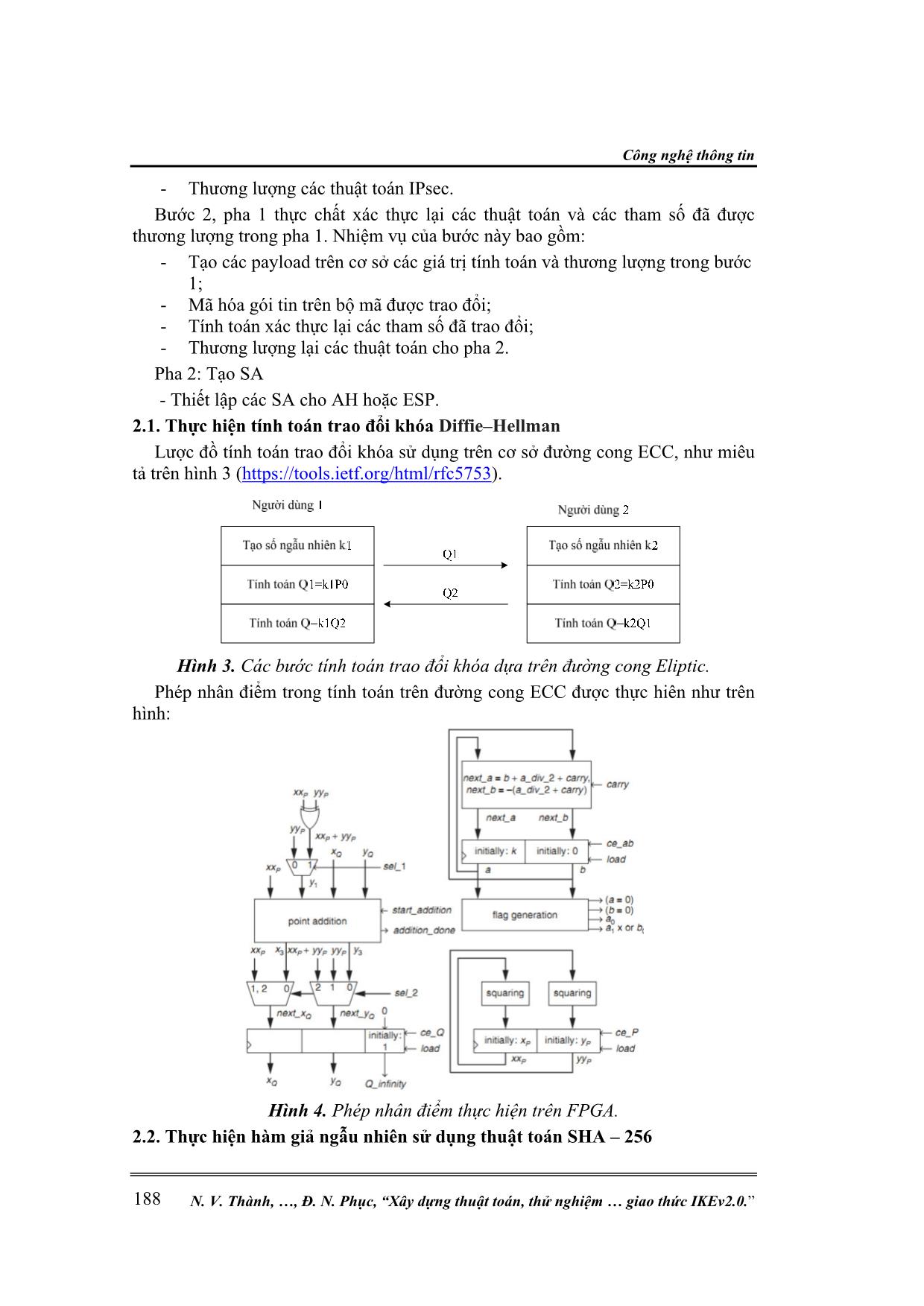

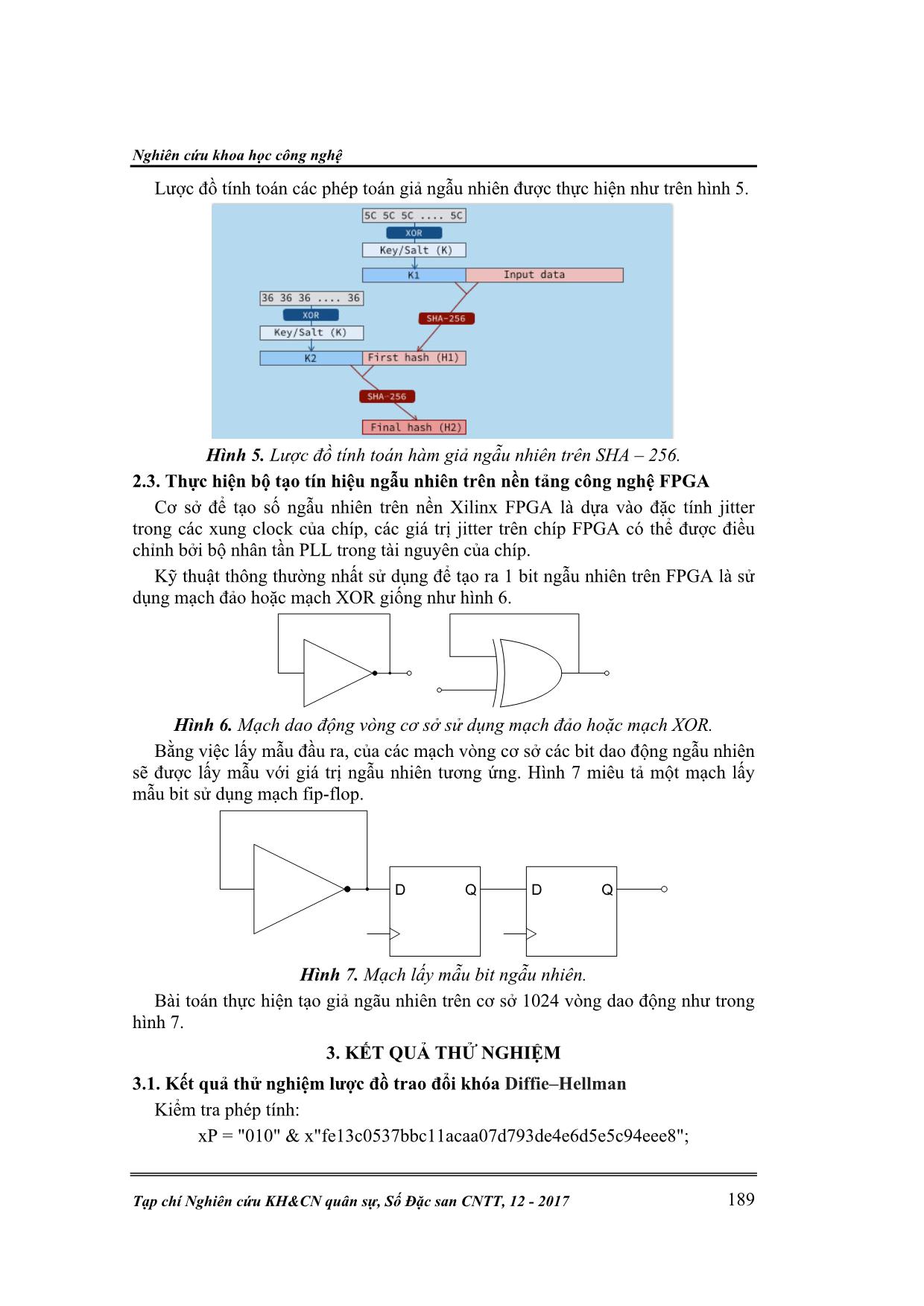

Giao thức IKEv20 thông thường được thực hiện trên phần mềm và sử

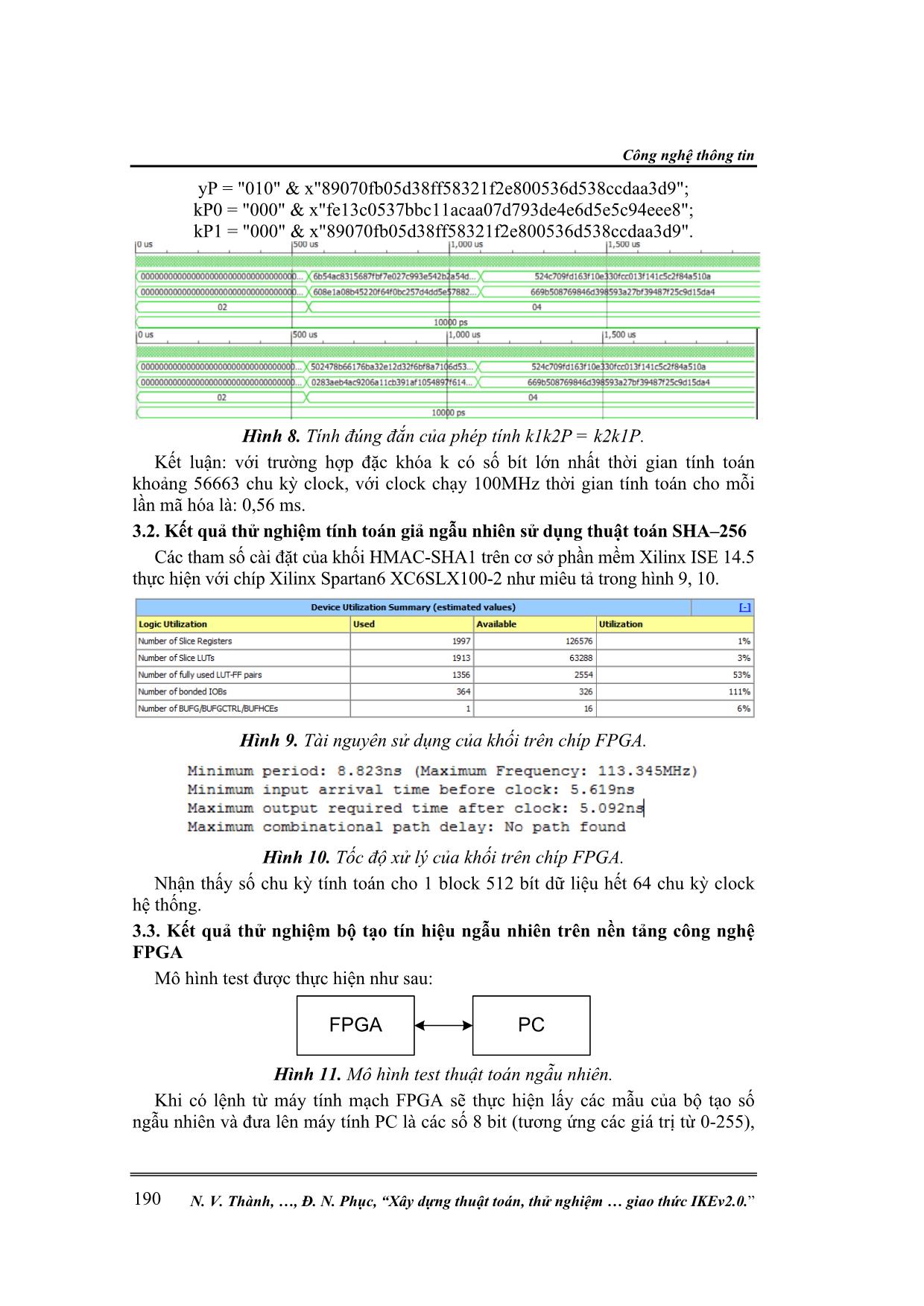

dụng mã nguồn mở. Bài báo đưa ra lược đồ cứng hóa giao thức trên nền công nghệ

FPGA để tăng độ mật, tăng tốc độ xử lý gói tin. Các giai đoạn của giao thức được

thực hiện theo nguyên lý xử lý song song và được cài đặt trên ngôn ngữ VHDL.

Giao thức có thể chạy trên các dòng chíp 6 Series, 7 Series của hãng Xilinx.

Xây dựng thuật toán, thử nghiệm đánh giá mô hình cứng hóa giao thức IKEv2.0 trang 1

Xây dựng thuật toán, thử nghiệm đánh giá mô hình cứng hóa giao thức IKEv2.0 trang 2

Xây dựng thuật toán, thử nghiệm đánh giá mô hình cứng hóa giao thức IKEv2.0 trang 3

Xây dựng thuật toán, thử nghiệm đánh giá mô hình cứng hóa giao thức IKEv2.0 trang 4

Xây dựng thuật toán, thử nghiệm đánh giá mô hình cứng hóa giao thức IKEv2.0 trang 5

Tải về để xem đầy đủ hơn

File đính kèm:

xay_dung_thuat_toan_thu_nghiem_danh_gia_mo_hinh_cung_hoa_gia.pdf

xay_dung_thuat_toan_thu_nghiem_danh_gia_mo_hinh_cung_hoa_gia.pdf