Bài giảng VDHL - Chương 3: Thiết kế mạch Logic tổ hợp bằng VHDL

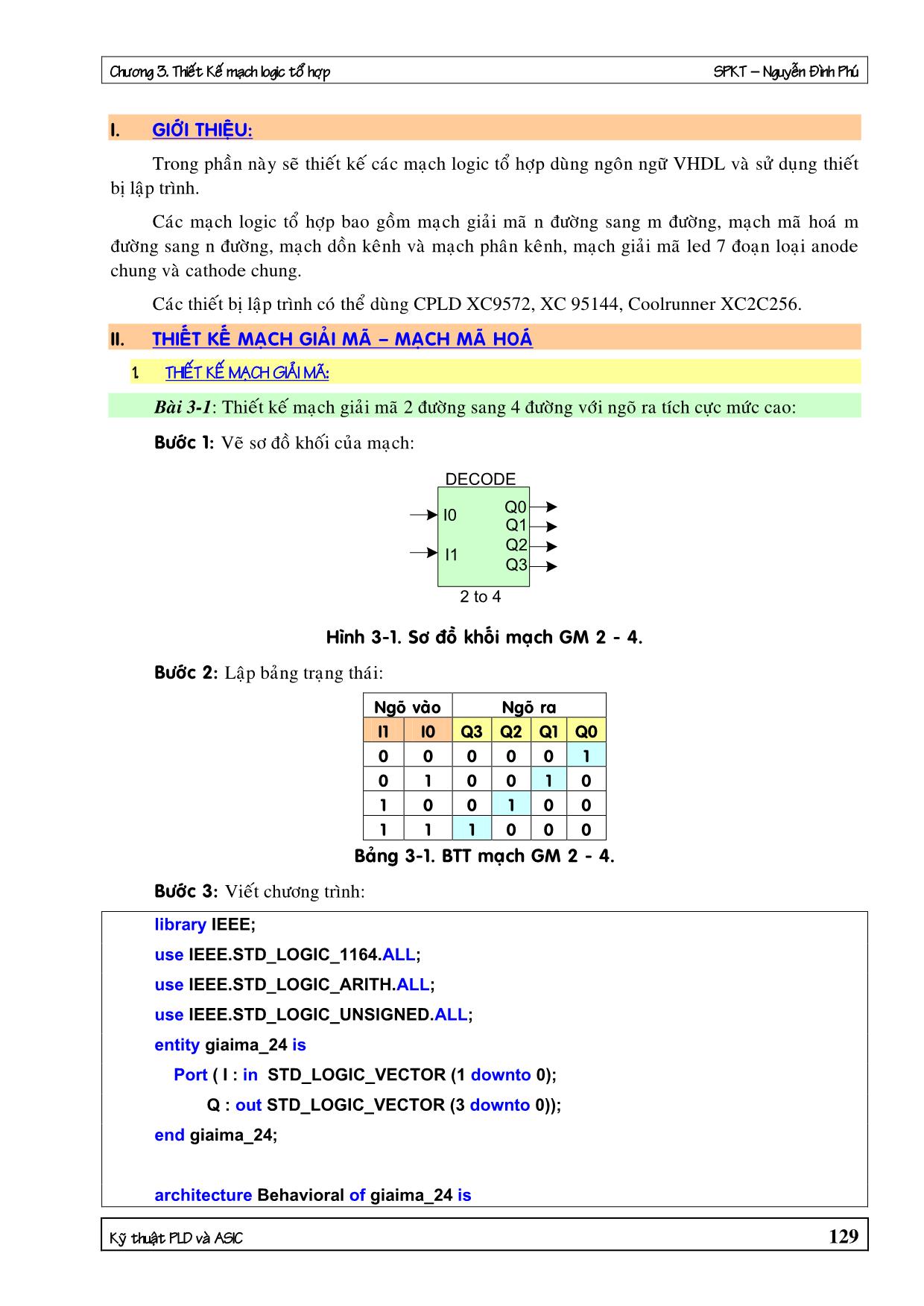

Trong phần này sẽ thiết kế các mạch logic tổ hợp dùng ngôn ngữ VHDL và sử dụng thiết

bị lập trình.

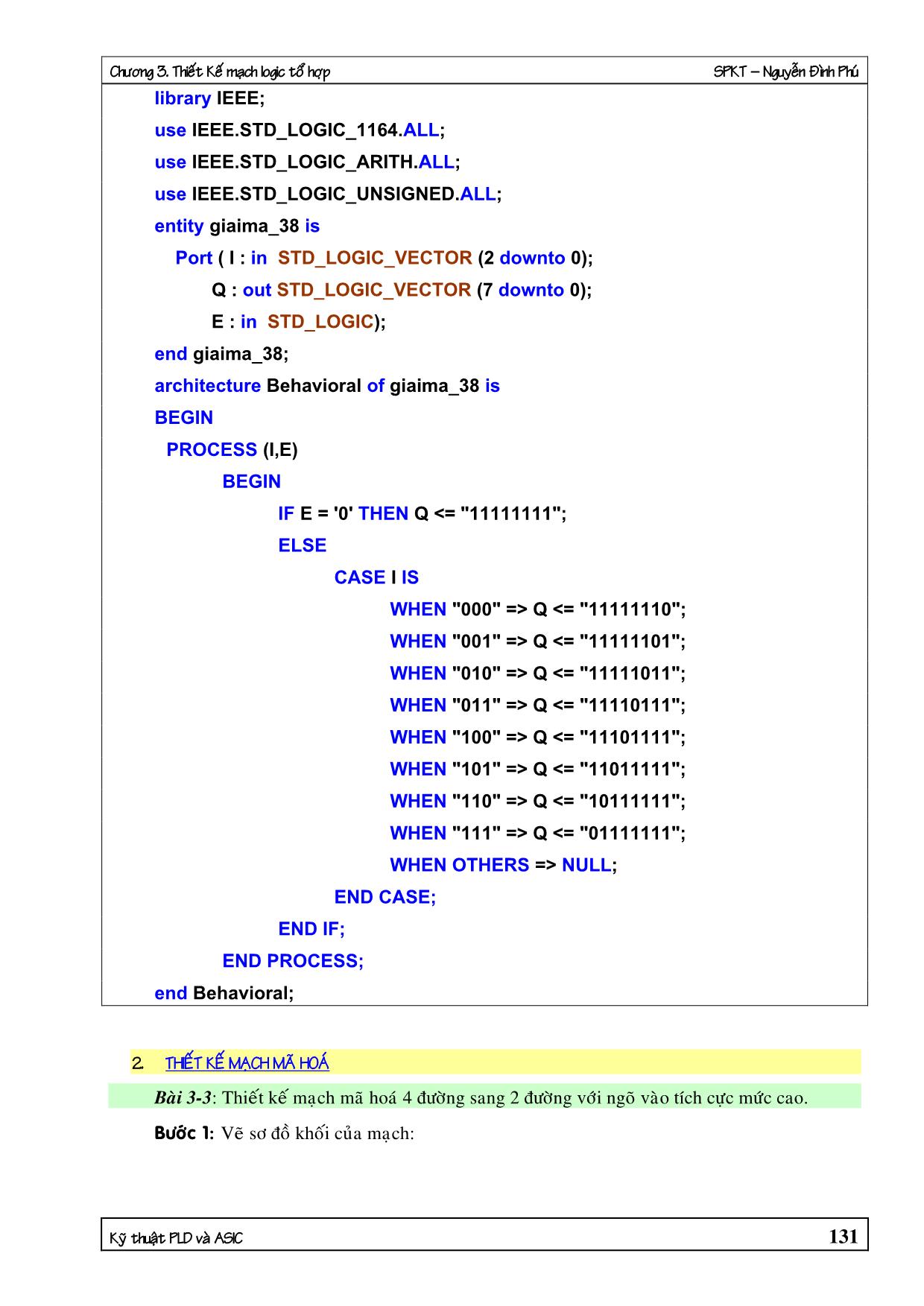

Các mạch logic tổ hợp bao gồm mạch giải mã n đường sang m đường, mạch mã hoá m

đường sang n đường, mạch dồn kênh và mạch phân kênh, mạch giải mã led 7 đoạn loại anode

chung và cathode chung.

Các thiết bị lập trình có thể dùng CPLD XC9572, XC 95144, Coolrunner XC2C256

Bài giảng VDHL - Chương 3: Thiết kế mạch Logic tổ hợp bằng VHDL trang 1

Bài giảng VDHL - Chương 3: Thiết kế mạch Logic tổ hợp bằng VHDL trang 2

Bài giảng VDHL - Chương 3: Thiết kế mạch Logic tổ hợp bằng VHDL trang 3

Bài giảng VDHL - Chương 3: Thiết kế mạch Logic tổ hợp bằng VHDL trang 4

Bài giảng VDHL - Chương 3: Thiết kế mạch Logic tổ hợp bằng VHDL trang 5

Tải về để xem đầy đủ hơn

File đính kèm:

bai_giang_vdhl_chuong_3_thiet_ke_mach_logic_to_hop_bang_vhdl.pdf

bai_giang_vdhl_chuong_3_thiet_ke_mach_logic_to_hop_bang_vhdl.pdf